(2124)[Total No. of Questions - 8] [Total No. of Printed Pages - 3]

1625

M. Tech 1st Semester Examination Design of Electronics System EC-102

Time: 3 Hours

Max. Marks: 100

sheet will be issued. \_ook (40 pages) issued to them and no supplementary/continuation The candidates shall limit their answers precisely within the answer-

Note: (i) Assume suitable data wherever necessary.

(ii) Attempt Any FIVE Questions

- (a) approximation ADC in terms of accuracy conversion Explain the successive approximation ADC with a suitable speed and resolution. What is the resolution of 12 bit diagram. Compare dual slope ADC and successive successive approximation ADC?

- **b** sequential circuits? What do you mean by hazard free asynchronous

- 0 How many comparators are required to design 12-bit flash type ADC?

- (a) Implement the following Boolean function with only one 4X I MUX

$F(A, B, C, D)=\Sigma m (0,2,3,6,8,9,12,14)$

(b) Design 24-bit comparator using six 7485 comparators in (10)(10)

two levels

(b) List the application of Pl.A.

4

- (c) Realize EX-OR gate using only four NAND gates. Also realize Full-Adder circuit using only NAND gates. (8)

- (a) Design a BCD to Excess-3 code converter and implement using suitable PI.A. (15)

- (b) Write the design procedure for synchronous counter. Also design MOD-5 ripple counter. (5)

- 5. (a) Carry out the following conversion:

- (i) Convert a SR-latch to T Flip-Flop

- (ii) Convert JK to SR flip-Flop

(10)

- (b) Draw and explain the clocked SR Flip-flop in detail. (5)

- (c) Write notes on bounce elimination switches. (5)

- 6. (a) Write the design procedure for asynchronous counter.

Also design MOD-6 ripple counter. (8)

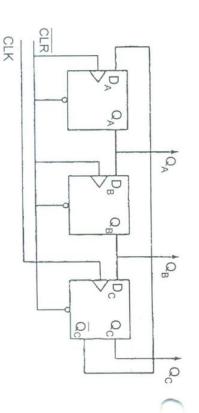

- (b) Analyze the sequential circuit as shown in Fig. 1. (12)

Fig. 1

- 7. (a) Explain the method to eliminate static hazards in asynchronous circuits with an example. (10)

- (b) Write notes on:

- (i) Electromagnetic Interference and Electromagnetic compatibility.

- (ii) Grounding and shielding of digital circuits. (10)

- (a) Design a 3-bit binary UP/DOWN counter with a direction control M. Use JK flip-Hops. (8)

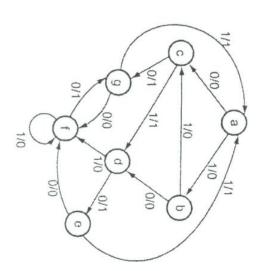

- (b) Design a clocked sequential circuit for state diagram as shown in Fig. 2. (Use state reduction technique). Use D flip-flop. (12)

Fig. 2